# UNIVERSITY<sup>OF</sup> BIRMINGHAM

# University of Birmingham Research at Birmingham

# **CHERI-TrEE**

Van Strydonck, Thomas; Noorman, Job; Jackson, Jennifer; Dias, Leonardo; Vanderstraeten, Robin; Oswald, David; Piessens, Frank; Devriese, Dominique

DOI.

10.1109/EuroSP57164.2023.00070.

License:

Other (please specify with Rights Statement)

Document Version

Peer reviewed version

Citation for published version (Harvard):

Van Strydonck, T, Noorman, J, Jackson, J, Dias, L, Vanderstraeten, R, Oswald, D, Piessens, F & Devriese, D 2023, CHERI-TrEE: Flexible enclaves on capability machines. in *EuroS&P - 8th IEEE European Symposium on Security and Privacy*. IEEE European Symposium on Security and Privacy, IEEE, pp. 1143-1159, 8th IEEE European Symposium on Security and Privacy, Delft, Netherlands, 3/07/23. https://doi.org/10.1109/EuroSP57164.2023.00070.

Link to publication on Research at Birmingham portal

Publisher Rights Statement:

© 2023 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. The final published version is available at https://doi.org/10.1109/EuroSP57164.2023.00070

**General rights**

Unless a licence is specified above, all rights (including copyright and moral rights) in this document are retained by the authors and/or the copyright holders. The express permission of the copyright holder must be obtained for any use of this material other than for purposes permitted by law.

- •Users may freely distribute the URL that is used to identify this publication.

- •Users may download and/or print one copy of the publication from the University of Birmingham research portal for the purpose of private study or non-commercial research.

- •User may use extracts from the document in line with the concept of 'fair dealing' under the Copyright, Designs and Patents Act 1988 (?)

- •Users may not further distribute the material nor use it for the purposes of commercial gain.

Where a licence is displayed above, please note the terms and conditions of the licence govern your use of this document.

When citing, please reference the published version.

Take down policy

While the University of Birmingham exercises care and attention in making items available there are rare occasions when an item has been uploaded in error or has been deemed to be commercially or otherwise sensitive.

If you believe that this is the case for this document, please contact UBIRA@lists.bham.ac.uk providing details and we will remove access to the work immediately and investigate.

Download date: 03. May. 2024

# **CHERI-TrEE: Flexible enclaves on capability machines**

Thomas Van Strydonck\*§, Job Noorman\*, Jennifer Jackson†, Leonardo Alves Dias† Robin Vanderstraeten‡, David Oswald†, Frank Piessens\*, Dominique Devriese\* \*KU Leuven †University of Birmingham ‡Vrije Universiteit Brussel

Abstract—This paper studies the integration of two successful hardware-supported security mechanisms: capabilities and enclaved execution. Capabilities are a powerful and flexible security mechanism for implementing fine-grained memory access control and compartmentalizing untrusted or buggy software components. Capabilities have a long history but have gained significant momentum recently, as evidenced by ARM's experimental Morello processor that supports the Capability Hardware Enhanced RISC Instructions (CHERI). Enclaved execution is a popular mechanism for dynamically creating Trusted Execution Environments (TEEs), called enclaves. Enclaves are isolated execution contexts that protect the integrity and confidentiality of software in the enclave (even against compromised system software) and that support attestation.

Integrating capabilities and enclaved execution in a single processor is challenging because they overlap partially in their security objectives, and a clean integration should unify the way in which these overlapping objectives are achieved. In addition, it is not obvious how attestation should interact with capabilities. In this paper, we propose CHERI-TrEE: a novel design for a processor that cleanly integrates support for both capabilities and enclaved execution. CHERI-TrEE targets low-end embedded systems without virtual memory. We show that CHERI-TrEE is greater than the sum of its parts by showing how it naturally supports useful features that have traditionally been hard to support in enclaved execution, like dynamically growing and shrinking enclaves, non-contiguous and nested enclaves, sharing of memory between enclaves etc. We implement our proposal both in hardware on a RISC-V processor, as well as in a small software hypervisor on top of ARM Morello, and evaluate impact on performance and hardware resources.

Index Terms—enclaves, TEE, trusted execution, capability machines, CHERI, CHERI-RISC-V, ARM Morello

# 1. Introduction

There is a wide variety of hardware-supported mechanisms to securely isolate software, each with its strengths and limitations. This paper studies the integration of two related but fundamentally different mechanisms: capabilities and enclaved execution.

Capabilities are unforgeable tokens of authority granting rights to system objects. They are a powerful security mechanism for implementing fine-grained access control and for compartmentalizing untrusted or buggy

software components. Capability machines implement the concept of capabilities at the machine code level: they provide hardware support for capabilities by defining an instruction set architecture (ISA) that provides access to system memory only through memory capabilities, a kind of hardware-supported fat pointers. The ISA is designed to ensure that software can only create capabilities that represent a subset of the authority that the software already holds. Hence, capabilities are a secure basis for implementing memory access control and isolation. Next to memory capabilities, capability machines can support a wide variety of other kinds of capabilities, including, for example, object capabilities that can control access to software defined objects, or sealing capabilities that can symbolically encrypt or decrypt other capabilities. Capability machines have a long history [1], but have gained significant momentum over the last decade with, for instance, the development of the CHERI system [2], and with the ARM Morello project [3] that integrates the concepts of CHERI in the widely used ARM architecture.

Enclaved execution is a security mechanism that supports the run time creation of enclaves, execution environments for software components that are strongly isolated and that can attest their identity to other code running either locally on the same platform or remotely on other platforms. The idea of Enclaved Execution Systems (EES) is more than a decade old [4], and currently many implementations are available [5], [6], [7], [8], [9], [10], both in research prototypes, as well as in commercial systems like Intel's Software Guard Extensions (Intel SGX). We will therefore use the term enclave to designate a general protected module, rather than SGX-like enclaves specifically, as sometimes happens in the literature.

**Problem statement.** Assume the designer of an embedded system has decided to use a capability processor (we motivate the use of capabilities on embedded processors below). This paper then aims to find the best way to integrate enclaved execution into the capability processor design. This is challenging because (1) these mechanisms overlap partially in their security objectives (for instance, both mechanisms provide their own form of controlled invocation) and a clean integration should unify how these overlapping objectives are achieved, and because (2) it is not obvious how (remote or local) attestation should interact with capabilities.

To the best of our knowledge, this paper is the first to propose a design that cleanly integrates both mechanisms in a single processor ISA. Roughly speaking, our design proceeds as follows: enclaved execution is known to be a *complex* security mechanism [11], hence we first decom-

pose it into a set of maximally independent primitives. Next, we implement these primitives on top of the state-of-the-art CHERI capability machine [2], [12], maximally reusing existing CHERI mechanisms. For instance, enclave isolation reuses standard CHERI object capabilities. The new mechanisms we introduce are lightweight, orthogonal, and contribute features that do not yet exist in CHERI. They allow (1) obtaining guarantees about exclusive ownership of a memory region (i.e., no other code on the system has a reference to said memory), and (2) obtaining sealing capabilities (a private key used to symbolically encrypt or sign other capabilities) derived from an enclave's identity.

We demonstrate that the resulting system, CHERI-TrEE, can be used as an EES, allowing other code on the system to establish trust in an enclave. CHERI-TrEE is greater than the sum of its parts. Our reuse of existing CHERI features achieves economy of mechanism and reduces complexity and cost. At the same time, the resulting EES innately supports features that have traditionally been hard to accommodate in EESs: dynamically growing and shrinking enclaves, non-contiguous enclaves, nested enclaves, sharing of memory between enclaves, etc.

**Target systems.** Capabilities and enclaved execution have been studied for both low-end embedded systems and higher-end systems that support virtual memory or virtualization instructions. In this paper, we focus on low-end embedded systems without virtual memory. Although we demonstrate an implementation on top of ARM Morello, a high-end architecture, this proof-of-concept implementation does not use virtual memory and is to be interpreted (for the time being) as a proof of feasibility of a software-only implementation of CHERI-TrEE.

Note that there are already good arguments for applying CHERI-like primitives to embedded processors, independently of CHERI-TrEE. The benefits and costs of CHERI-like protection (compared to e.g., MPUs) on embedded systems have been studied extensively in the literature [13], [14], [15]. CHERI-TrEE is intended to additionally offer EES security primitives when CHERI protection is already used on an embedded system for its other benefits. As such, the costs of supporting CHERI-TrEE should be regarded separately from the costs incurred by adding support for capabilities to the processor.

Attacker model. As usual for EESs, we assume an attacker that can control *all* software present on the system, notably including privileged software such as the operating system. CHERI-TrEE can be implemented in either hardware, software, or a mixture thereof. Depending on this choice, a small software interrupt handler and a small hypervisor might be considered trusted. Other desirable enclave properties that are largely orthogonal to capabilities are left out of scope: availability guarantees, hardware-based attacks (cold-boot attacks, malicious DRAM, ...) or side-channel attacks (timing or cache side-channels, memory bus snooping, ...). Note that this assumption inherently limits the size of our TCB compared to systems with a stronger attacker model, that implement additional security features (e.g., memory encryption).

**Contributions.** To summarize, in this paper we contribute:

- A decomposition of enclaved execution into more basic primitives.

- The design of CHERI-TrEE, a capability-based ISA extension that supports these primitives and hence integrates capabilities and enclaved execution.

- A specification and security argument for classic enclaved execution operations (initialization, unloading, local attestation, secure communication) on top of CHERI-TrEE.

- An open-source implementation of CHERI-TrEE on top of RISC-V, including a Sail specification of the ISA and a hardware implementation on FPGA, as well as a proof-of-concept implementation on ARM Morello [3].

Our evaluations and benchmarks are open source.

- An evaluation of the impact on performance and hardware resources of the extension on the considered platforms.

For reasons of anonymity, we cannot provide the implementation sources during the review process. Files can be made available to reviewers on request.

# 2. Background

We implement all EES primitives by extending CHERI-like capability machines [2]. We thus briefly recap the background on enclaved execution and capabilities.

### 2.1. Enclaved execution

Enclaved execution is a security mechanism that enables *secure remote computation* [16] with a small Trusted Computing Base (TCB). It supports the runtime creation of *enclaves*, strongly isolated software components that can attest their identity to other code running either locally on the same platform or remotely on other platforms. A number of variations on this idea have been designed and implemented by researchers [4], [6], [9], [8], [10], and Intel have commercially implemented the Software Guard Extensions (Intel SGX). We provide an overview of existing designs in Section 7.

The typical life cycle of an enclave goes as follows: First, untrusted code creates the enclave and initializes it from a static binary code image (e.g., a .dll file). After initialization, the enclave is supposed to be isolated from all other (non-TCB) software, and has an enclave identity based on the code image initially loaded. At this point, interaction with the enclave is possible: the enclave context (untrusted code and/or other enclaves) can call into the enclave, and the enclave can call out to its context. Such interactions can be authenticated: the context can get proof of the identity of an enclave (attestation), and similarly, the enclave can get proof of the identity of other enclaves calling in. Most EESs extend attestations to remote platforms: a remote party can get proof of the identity of an enclave it is interacting with. Finally, an enclave can be terminated. Care must be taken to ensure that enclave secrets do not leak on termination.

Existing EESs vary widely in the implementation details of this life cycle. There are differences in the way isolation is implemented, in the interaction with other isolation mechanisms (like virtual memory), and in how termination is handled. However, all existing systems face challenges in securely handling natural features, including: nesting of enclaves, non-contiguous enclaves, dynamic enclave memory (de-)allocation, efficient memory sharing between enclaves, the number of supported enclaves, etc.

# 2.2. Capability machines and CHERI

Capability machines define an ISA that provides access to system memory only through memory capabilities, a kind of unforgeable hardware-supported fat pointers that carry metadata about the bounds over which they grant authority. The ISA is designed to enforce monotonicity of authority: software cannot forge capabilities that increase the access to memory that it initially possessed. Hence, capabilities can be used to enforce memory access control and isolation; properties we will rely on when designing secure enclaves in Section 3. The base platform on which we build our design is a variant of CHERI-RISC-V. The CHERI-RISC-V capability metadata relevant for this paper includes base and length fields, otype, permissions and an address field. A memory capability can be used in store and load instructions to access its address, provided the address is in the range [base, base+length], and compliant with the permissions specified in the permissions field (e.g., read, write, execute). The ISA provides instructions to inspect and modify metadata fields, but only in ways that respect the aforementioned monotonicity of capability authority. For instance, bounds can be reduced but not expanded, e.g., the CSetBoundsExact cd, cs1, rs2 instruction takes an existing capability in cs1 and a new bound length in rs2, which must be equal to or less than the length of cs1, and creates a new capability in cd with the specified bound length.<sup>3</sup>

CHERI supports other kinds of capabilities besides memory capabilities, for which the interpretation of the metadata and the possible uses vary. Notable for our purposes are so-called *sealed capabilities* [2], a type of CHERI capability that cannot be used in operations like stores and loads or have its fields altered; only reading fields is allowed. Sealed capabilities are sealed with a specific seal (i.e., a key), represented by a value in the otype field. The highest otype value represents an unsealed capability.

Capabilities can be sealed and unsealed through the CSeal and CUnseal instructions. The CSeal cd, csl, cs2 instruction takes unsealed capabilities in csl and cs2, and seals csl with otype equal to the address field of cs2, placing the result in cd. To avoid arbitrary capabilities being used to seal other capabilities, cs2 must have the bespoke Permit\_Seal permission bit set, which allows it to seal other capabilities with otypes within its bounds. The CUnSeal cd, csl, cs2 instruction is the dual of CSeal; csl must now be sealed, and cs2 is required to have the Permit\_UnSeal permission bit set. The otype in the address field of cs2 must match the otype of csl. The unsealed result is placed in cd. Software cannot bypass the security guarantees

offered by sealed capabilities: as capability authority must evolve monotonously, not even privileged software can set the Permit\_Seal/Unseal bits or forge sealed capabilities.

The purpose of these capabilities in CHERI is dual. First, otypes can be used to implement efficient symbolic encryption and signing, using the aforementioned permission bits. A capability that has both Permit\_Seal and Permit\_UnSeal bits set can be used for symmetric encryption, because it can both encrypt (seal) and decrypt (unseal) messages (capabilities). If a capability carrying the Permit\_Seal permission is made public and a Permit\_UnSeal counterpart is kept private, we get public key encryption. The converse setup results in a digital signature scheme. These observations form the basis of our design for secure enclave communication in Section 3.2.

Secondly, sealed capabilities can be used to implement the aforementioned object capabilities that control access to software defined objects. The CInvoke cs1, cs2 instruction enables this functionality and permits secure domain transitions. If both cs1 and cs2 contain capabilities with matching otypes and solely cs1 has execute permission, then the two capabilities are atomically unsealed, and cs1 is installed in the program counter register, continuing execution from the invoked domain. Together, cs1 and cs2 are said to constitute a sealed pair, with cs1 the code and cs2 the data capability. Such pairs can safely be passed to adversarial code, as both capabilities are sealed and can only be invoked together. To distinguish sealed pairs from other sealed capabilities, a permission Permit\_CInvoke determines whether sealed capabilities can be invoked together. We will use sealed pairs to perform secure domain transitions into enclaves in Section 3.2.

# 3. The design of CHERI-TrEE

In this section, we propose decomposing the requirements for enclaved execution into orthogonal properties (Section 3.1). These properties serve as a guideline for the design of CHERI-TrEE, our capability-based EES. Section 3.2 considers the CHERI capability machine as a starting point and lists for each property whether it can be enforced through existing capability primitives or whether extensions have to be defined. With this analysis in hand, Section 3.3 discusses the security model and the operations offered by the TCB in a backend-agnostic way. Section 3.4 discusses implementation details that Section 3.3 brushed over, and Section 3.5 contains an abstract discussion of why our design ensures isolation and secure communication. Finally, Section 3.6 highlights how our bottom-up approach, maximally reusing the flexibility of architectural capabilities, allows for greater flexibility than the state of the art.

Capabilities and enclaved execution have been studied for systems that support virtual memory and systems with a single physical memory address space. This paper focuses on the latter kind of system. The combination with virtual memory and address translation brings additional challenges that are left for future work discussed in Section 6.

<sup>2.</sup> As in the RISC-V and CHERI specifications, we use rs1 and rs2 for source and rd for destination integer registers, while using cs1, cs2, and cd for capability registers throughout this paper.

<sup>3.</sup> Assuming the requested bounds can be represented in CHERI's compressed capability representation.

# 3.1. Decomposing enclaved execution into core properties

In our view, the core security properties required to build an EES can be decomposed into the five categories listed below. Some other properties (e.g., confidential deployment [9], secure storage) are also relevant, but either not essential to the construction of a *functional* EES, or outside our attacker model. The core properties are:

- (1) **Exclusive access**: A mechanism to guarantee exclusive access to specific memory areas is required for the secure initialization of an enclave. In principle, the enclave can be allowed to share its uniquely owned memory once it has been securely initialized, but few enclaved execution systems support this. For example, Intel SGX relies on *Processor Reserved Memory* and the initialization process to guarantee exclusive access, while Sancus relies on program-counter based access control.

- 2 Controlled invocation: To avoid reasoning about the correctness and security of many possible control-flow paths, enclaves can only be invoked at predefined *entry points*. Examples are *ecalls* in Intel SGX and *entry points* in Sancus. In most systems, entry points are declared at enclave creation time, but at least conceptually, new entry points could also be created dynamically.

- 3 Enclave identities and attestation: To enable multi-enclave/distributed applications, enclaves and third parties require a mechanism to establish trust in the correct initialization and execution of another enclave. This authentication process, called attestation, occurs either locally or remotely. It requires a notion of enclave identity, usually based on a cryptographic hash of the enclave code and metadata. Locally, the architecture provides a mechanism to communicate identities and authenticate enclaves to other code running on the same platform. Remote attestation requires cryptographic support, either in the form of a public key infrastructure (as in Intel SGX) or a symmetric key derivation scheme (as in Sancus).

- 4 Secure communication: A mechanism to securely communicate between two enclaves, both locally and remotely, is essential to achieve integrity and confidentiality. Locally, either CPU registers or shared memory can be used. Because enclaves might be deinitialized and replaced at any point, encrypting and signing messages cryptographically is required to ensure integrity and confidentiality. The efficiency of the involved cryptography is performance-critical. To avoid having to sign and encrypt messages, some EESs have built-in mechanisms to check liveness of the sender and receiver enclave. Here, time-of-check to time-of-use (TOCTOU) attacks can be an issue (e.g., for Sancus). For the remote case, the key distribution infrastructure of attestation can often be reused for secure communication with standard protocols.

- 5 Secure interruptability: When an enclave's execution is interrupted, its register state should not be accessible to untrusted code as this potentially breaks confidentiality guarantees offered by the enclave. Additionally, the enclave's register state must be correctly and securely restored after servicing the interrupt.

Because capabilities provide no protection during network transition, the design of remote attestation and remote secure communication would mostly reuse existing solutions. The remote aspects of enclaved execution are therefore left for future work and further discussed in Section 6.

# 3.2. Satisfying the security properties

We now discuss how we enforce these properties in our design that builds on CHERI, reusing CHERI primitives where possible ( ) and extending the TCB otherwise ( ). In the remainder of Section 3, the TCB is taken to be hardware-only (except for a small software interrupt handler). However, Section 4.4 illustrates that this is not required.

- Exclusive access at runtime is not supported out of the box in CHERI, so we add *memory sweep* functionality to the TCB. During a memory sweep, the TCB checks the whole memory and all architectural registers (including special registers) for the presence of capabilities that overlap with a given capability. To successfully complete enclave initialization, the unique ownership of an enclave's code and data sections needs to be verified through such a sweep. The memory sweep is a simple solution to exclusive access that can be optimized further and for which alternatives exist. We discuss these in more detail in Section 6.

- Controlled invocation can be implemented using the aforementioned sealed capability pairs [2]. Concretely, if the enclave only shares sealed capabilities to specific entry points with adversary code, then capability monotonicity ensures that the enclave cannot be otherwise entered. Alternatively, controlled invocation can be implemented through so-called *enter capabilities* [17], which intuitively combine both the code and data capabilities of a sealed pair into a single capability. This alternative could have simplified a few aspects of our design, but we did not implement it, as enter capabilities have only recently been added to CHERI.

- Enclave identities and attestation are not built into CHERI. The architecture hence has to use a cryptographic hash function to calculate an enclave's identity by hashing the code section. Additionally, to enable local attestation, an instruction needs to be added to securely look up this generated identity.

- Secure communication can be efficiently implemented locally through the symbolic encryption provided by sealed capabilities. Every enclave has a signing capability cap\_sign with otype o\_sign in its address and both Permit\_Seal and Permit\_UnSeal set. The enclave solely shares the Permit\_UnSeal part of this capability with other code, so that it can exclusively authenticate its messages and other enclaves can verify them. Although it might seem unintuitive that a capability (rather than just the integer otype o\_sign) is required to verify a signature, without this capability, recipients of signed values would have no way to remove the signature and access the payload underneath. Dually, the enclave has an encryption capability cap\_enc with otype o\_enc and shares only its Permit\_Seal part so that only the enclave can decrypt messages encrypted with o\_enc. We refer to the shared halves of both capabilities as an enclave's public keys, and to the full-authority versions as its private keys.

- Secure interruptability cannot be guaranteed in the presence of an untrusted interrupt handler: the confi-

dentiality and integrity of an enclave depend on an adversarial interrupt handler not being able to read security-critical capabilities (e.g., the capability for the data section or cap\_sign) from its register state. We resolve this problem by installing a minimal, trusted interrupt handler that cannot be altered or bypassed by untrusted code. The handler performs the necessary register sanitization before passing control to the adversary and restores the register state on return. This solution is similar to the security monitor employed in Keystone [10], but our handler is more limited in scope (e.g., it does not need to manipulate memory protection state). Although we currently implement interrupt handling in software as a proof of concept, a Sancus-style hardware implementation is entirely feasible.

# 3.3. Fleshing out the design

Having studied the security of enclaves at a conceptual level in Sections 3.1 and 3.2, this section now discusses the modifications we made to the CHERI architecture to implement our design.

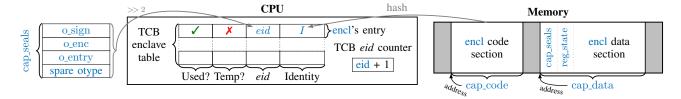

Our first addition to the TCB is the enclave table in Fig. 1, which connects enclave identities to their otypes. The table enables local attestation: a new operation performs a secure lookup of the enclave identity associated with an otype that was received from untrusted code.

Each enclave entry in the table contains three otypes: the aforementioned otypes o\_enc and o\_sign, that serve as otypes for the enclave's cap\_enc and cap\_sign capabilities, and an otype o\_entry that will be used to create a sealed entry point from the enclave's unsealed code and data section. We allocate these otypes such that they are consecutive and 2-bit-aligned. This allows the TCB to store only the common prefix in the enclave table, which we call the enclave identifier (eid) and allows an enclave to represent ownership of all three otypes in a single capability cap\_seals (cf. Fig. 1).

We ensure that otypes are spatially and temporally unique to avoid collisions with previously allocated enclaves and other usages of sealed capabilities. In case otypes are required for other purposes on the capability machine, the otype space should be split up.

We now study the operational aspects of our design in more detail. We discuss (de)initialization, local attestation, communication between enclaves, stand-alone memory sweeps and secure interrupts.

**Initialization.** Enclaves register themselves with the TCB by invoking an initialization operation, passing capabilities cap\_code and cap\_data as arguments. Initialization will perform the following steps:

- 1. Perform a memory sweep to check unique ownership of cap\_code and cap\_data.

- 2. Allocate fresh otypes for the enclave and store the capability cap\_seals for them to the start of cap\_data so that the enclave can set up its symbolic encryption upon invocation.

- Use o\_entry to seal cap\_code and cap\_data, transforming them into a sealed pair and ensuring controlled invocation.

- 4. Compute the enclave's identity I by hashing its code section.

5. Store this identity *I* in the TCB along with its *eid* to allow secure lookups. If the TCB is full, the instruction fails

After successful completion, the enclave has been initialized and the TCB contains an appropriate entry (cf. Fig. 1, we explain the *Temporary* field below). Untrusted code can now invoke the enclave by executing CInvoke on cap\_code and cap\_data.

Upon first invocation, the enclave's code will initialize any necessary state and enable symbolic encryption by returning the public parts of its sealing and encryption keys. The enclave can create a so-called *fast entry point* at a different offset to skip initialization on subsequent invocations (taking care that the initial entry point does not reinitialize the enclave if it is invoked again).

Deinitialization. A TCB operation deinitialize allows an enclave to deregister itself. The enclave authenticates itself by providing its cap\_seals capability (with both Permit\_Seal and Permit\_UnSeal permissions set). Thus, only the enclave itself or parties that were granted access to (subranges of) cap\_seals can deinitialize it. After deinitialization, an enclave can clear sensitive data (including its seals) and return the capabilities for its code and data section to untrusted code. As in Sancus, a processor reset is required to deinitialize rogue enclaves. A processor reset is also required to reuse the otypes of decommissioned enclaves, since we do not support memory sweeps to reclaim otypes.

Local attestation. An enclave gets access to another enclave's entry points and public encryption/signing keys by e.g., retrieving them from an (untrusted) enclave registry. Regardless of the origin, enclaves require a way to verify that an otype corresponds to an enclave of interest. The TCB offers a local attestation operation that takes an otype and returns the enclave identity of the corresponding enclave (by storing it to memory through a provided capability). Note that when an enclave calls into another enclave, the callee is not required to attest the caller ahead of time. Indeed, the caller can pass its public keys along with the arguments, so the callee can perform local attestation of the caller while processing the call.

**Secure communication.** Different primitives combine to secure communication between enclaves. First, any confidential arguments or return values are *encrypted* with the recipient's public encryption key. Additionally, as capabilities carry authority, even non-confidential capability arguments and return values must be encrypted if their authority should not be made available to untrusted code.

Second, when returning from a call, the callee should *sign* (part of) the return value to allow the caller to confirm that its call was indeed processed by the callee. Conversely, the callee might also require the caller's signature to authenticate the caller; the callee could e.g. have a whitelist of enclaves whose requests it services. Lastly, to avoid replay attacks, the caller can make use of a *nonce* as part of its requests.

As the literature shows, it is possible (but difficult) to construct a wide variety of secure communication protocols using the available primitives (asymmetric encryption, signing, and nonces) [18]. Since our aim is to introduce a capability-based design for enclaved execution, not

Figure 1. Memory and TCB state after initialization of an enclave encl. The TCB's four enclave table fields indicate whether an entry is in use (Used?), whether it is temporary (Temp?), and record the enclave's identifier (eid) and identity (Identity). Importantly, the TCB does not track the enclave's memory layout, but solely connects the enclave's eid and identity to each other. All values relating to encl are typeset in blue; its identity (I), identifier (eid), code and data sections cap\_code and cap\_data, four assigned otypes, and their capability cap\_seals. The reg\_state region stores the enclave's register state during an interrupt. Gray arrows illustrate how I is obtained by hashing the code section and eid by right-shifting the otypes. Figure layout inspired by Noorman et al. [9].

design secure communication protocols on top, we defer the development of these protocols to future work.

**Separate memory sweep.** As we will discuss in Section 3.6, by offering the memory sweep functionality as a stand-alone operation as well, we can increase the flexibility of the enclave model. This operation performs a memory sweep for a given capability and outputs a boolean indicating success or failure.

Interrupt handling. For secure interrupts and system calls, we install a fixed, non-bypassable, trusted interrupt handler. When an enclave is interrupted, control passes to the trusted handler. This handler is responsible for storing enclave state to an enclave-designated location (before control is passed to an untrusted interrupt handler) and restoring the state afterwards. It includes measures to prevent reentrancy issues. Much like Keystone, we leave the extension of our scheme to a multi-threaded setting, as well as nested interrupts, attestation of the interrupt handler, and the delegation of synchronous interrupts and errors to an enclave-private interrupt handler to future work.

# 3.4. Technical details

Otypes and eid. As mentioned above, each enclave uses an eid to represent all of its otypes o\_sign, o\_enc and o\_entry. In fact, we reserve an additional fourth spare otype (cf. Fig. 1), which the enclave can use to e.g. create additional entry points, because four adjacent otypes share all but their last two bits. The TCB allocates four fresh seals by increasing a hardware counter (TCB eid counter in Fig. 1), failing when the otype space has been depleted. Any enclave otype is then efficiently convertible into the eid by a 2-bit right shift. Note that the specific role of each otype (except for o\_entry) is up to software convention.

For proper operation, we assume the otype space available to enclaves to be sufficiently large. This requirement is currently not met for CHERI Concentrate 64 (CC64), the compressed 64-bit representation of capabilities that CHERI defines for RV32 (32-bit RISC-V); only 4 bits are available for the otype field [19]. To resolve this issue, the CHERI specification contains a proposal to store otypes of sealed capabilities as metadata in memory instead of having the otype be in the capability itself [12]. For RV64 (64-bit RISC-V), 18 bits are available in CHERI Concentrate 128 (CC128), which poses fewer problems.

Invoking sealed capabilities as entry points. One might ask whether o\_enc or o\_sign could be reused instead of o\_entry to seal the entry point. The answer is negative; reusing o\_sign would allow adversaries to simply unseal the enclave's sealed code and data sections without calling CInvoke, whereas reusing o\_enc would allow the adversary to create their own code section, and use that to unseal the enclave's data section by executing CInvoke. For similar reasons, it is important that Permit\_CInvoke is unset on capabilities sealed with enclave encryption keys.

# Mapping TCB operations to RISC-V instructions.

Unfortunately, the initialization TCB operation is difficult to implement as a single instruction on a RISC ISA like RISC-V, where instructions generally have only one output operand. Initialization produces two outputs, because it has to overwrite both cap\_code and cap\_data with their now-sealed variants. To solve this, we split the operation into two separate instructions; EInitCode and EInitData, which initialize the enclave's code and data sections in two consecutive phases.

The EInitCode cd, csl instruction is called first, with cap\_code in csl. To ensure that the unsealed cap\_code is overwritten by its sealed counterpart, cd and csl are required to be equal. For efficiency reasons, EInitCode does not yet check uniqueness of cap\_code, as EInitData will perform a single sweep for cap\_code and cap\_data simultaneously. Computing the enclave's identity is also deferred until EInitData, since adversarial code might still have access to cap\_code.

Once the *eid* has been generated, <code>EInitCode</code> seals cap\_code with o\_entry, sets its address to its base (to avoid arbitrary entry offsets) and writes it to cd. <code>EInitCode</code> will generate the following *temporary* TCB entry (cf. Fig. 1), to be later finalized by <code>EInitData</code>, which does contain the enclave's <code>eid</code> but not its identity:

<code>/ / eid Don't care</code>. Note that <code>EStoreId</code> ignores TCB entries marked "temporary".

After EInitCode, the EInitData cd, cs1, cs2 instruction finalizes the enclave's initialization. It requires a sealed code section cap\_code (the result of calling EInitCode) in cs1, and an unsealed data section cap\_data in cs2. As before, cd and cs2 are required to be equal. The EInitData instruction now:

- 1. Looks up a temporary TCB entry with an *eid* corresponding to cap\_code's otype.

- 2. If found, checks unique ownership of cap\_code and cap\_data in a single memory sweep.

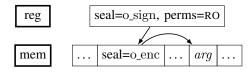

Figure 2. Combination of different security primitives: argument *arg* is encrypted with otype o\_enc, then signed with otype o\_sign.

- 3. Verifies that cap\_code does not contain any capabilities. Note that cap\_data *is* allowed to contain capabilities (including internal references to cap\_data/cap\_code), and is therefore not zero-initialized, as in e.g. Sancus.

- Calculates the enclave identity I as the hash of the contents of cap\_code, stores I in the temporary entry for eid, and marks the entry as permanent (cf. TCB state in Fig. 1).

- 5. Stores the cap\_seals capability in the first address of cap\_data. Writes cap\_data, sealed with o\_entry, to cd. Deinitialization is offered as a EDeInit rd, csl instruction taking cap\_seals in csl and indicating success or failure in rd. Similarly, local attestation is offered through an EStoreId rd, rsl, cs2 instruction, which takes an otype in rsl (any otype assigned to an enclave), and writes the identity of the corresponding enclave in the TCB (if any) to memory through the capability in cs2. The separate memory sweep is performed by the IsUnique rd, csl instruction, which takes its

input capability in cs1 and again indicates success in rd.

**Trusted exception handler.** The trusted exception handler uses the enclave's data capability cap\_data to save its register state into the reg\_state region (cf. Fig. 1). Then, it seals cap\_data using a unique, private otype o\_handler, places the result in a predefined register, and jumps to the untrusted interrupt handler. For this scheme to work, cap\_data should be present in a fixed register at all times. We use the idc (invoked data capability) register because it is atomically set to the unsealed data section when calling into an enclave using CInvoke. Once the untrusted code finishes servicing the interrupt, it returns to the trusted handler, which unseals the provided data section, restores the enclave's registers (apart from pc) and finally returns. The return should simultaneously reenable interrupts and restore the enclave's code capability. In the concrete case of RISC-V, the interrupt handler is installed in the mtvec register. It returns to the interrupted enclave through the mret instruction.

The tag of the pc capability stored in the reg\_state region effectively functions as an "is interrupted"-flag: the trusted handler sets it by storing an enclave's pc at interrupt time, and unsets it before returning to said enclave. This flag is used by enclaves to avoid reentrancy issues: if the tag is enabled when an enclave is invoked, the enclave simply returns. Additionally, the trusted handler uses the flag to avoid storing the registers of a previously interrupted enclave and restoring the registers of a non-interrupted enclave.

**Signing and encrypting simultaneously.** One might wonder how a capability with a single otype field can simultaneously represent encryption and signing. Fig. 2 illustrates that the solution is indirection: a memory argument *arg*

is first encrypted by an in-memory capability with otype o\_enc, which is in turn signed by a capability with otype o\_sign, present in one of the registers. This immediately illustrates one of the pitfalls of secure communication in our setting: messages are represented by capabilities rather than bit-strings. Copying a bit-string corresponds to a deep copy, whereas copying a capability creates an alias. This is the reason the top-most capability in Fig. 2 has read-only permission—if it allowed writes, an adversary could take a copy of the capability, remove the signature on the copy using the public signing key, and overwrite the underlying sealed capability. This would allow the adversary to create arbitrary capabilities, signed with a third party's seal. Similar concerns are at play when encrypting capabilities.

# 3.5. Security analysis

To summarize the above design, we now provide an analysis for why each stage of an enclave's lifetime respects exclusive access and secure communication. This assumes the enclave is correctly implemented and does not leak any of its private state.

- System boot: the system boots with an omnipotent capability. A small, trusted bootloader ensures that this omnipotent capability does not grant access to seals reserved for enclaves.

- Initialization: after initialization, the memory sweep guarantees us that no aliases for the enclave's entry point exist. Freshness of the generated seals ensures that no code has authority over the enclave's otypes.

- During operation: as long as the enclave does not leak its private state, no external code can unseal capabilities sealed by the enclave. Additionally, the enclave can distribute the public halves of its sealing and signing capabilities without compromising its security, because of the semantics of sealed capabilities.

- During interrupts: the enclave's register state is stored in its data section, which is sealed such that only the trusted interrupt handler can restore the enclave's state. Reentrancy is currently unsupported: an interrupted enclave simply returns upon further invocation.

- Deinitialization: the enclave erases its seals before returning its authority to the context. This ensures forward secrecy and authenticity of messages it encrypted and signed. Other secrets and capabilities in the data section are scrubbed on an application-specific basis.

Formal modeling and proof of these and other properties from Section 3.1 are left for future work.

## 3.6. Flexibility of our bottom-up design

There are two main reasons for the maximal reuse of existing capability primitives: First, the size of the TCB remains limited. Second, the resulting enclaves do not rely on the hardware to manage their authority but are self-governing, resulting in more flexible software-based design patterns. The cost of this flexibility is establishing unique ownership at runtime (i.e., the memory sweep) and an increased burden on the software developer to not leak security-critical capability authority. On the other hand, spatial memory safety does mitigate some API-level exploits of the types identified by Van Bulck *et al.* [20]. For example, if an enclave does not share any capabilities

pointing into its own memory with the adversary, then it does not require checks to ensure that pointers passed in from untrusted memory fall outside of its bounds, avoiding issues with improper implementation of these checks.

Although some EESs offer enclaves that are flexible in some of the below respects (see Section 7), the combination of different types of flexibility in our design, without requiring additional architectural changes, is novel. We support flexibility in the following ways:

**Growing, shrinking, nested and non-contiguous enclaves.** All of these are supported by our design because an enclave's footprint is not managed by the TCB, but rather determined by the capabilities it owns.

To grow an enclave, we employ the previously introduced IsUnique instruction. An enclave can request a sweep for a capability provided by untrusted code to verify unique ownership and add it to the enclave's memory footprint. In order to shrink, an enclave simply shares capabilities for part of its footprint with untrusted code.

In state-of-the-art EES, nesting enclaves (i.e., creating an enclave inside an existing enclave) is usually impossible because the hardware disallows enclave footprints from overlapping. One motivation for having nested enclaves is that it would allow for easy virtualization (inside an enclave) of code that itself uses enclaves. Nested enclaves can be initialized anywhere inside an enclave's uniquely owned memory. The only restriction is that the memory sweep fails if an external party holds a sealed pair for an entry point that overlaps with the nested enclave.

Enclaves can have non-contiguous footprints, e.g., to take exclusive ownership of an MMIO region mapped to a peripheral, reported to be impossible in Sancus [21].

Sharing memory. Sharing memory between enclaves amounts to simply sharing a capability for a uniquely owned memory region between said enclaves. No encryption is required. Once enclaves are done sharing memory, there needs to be a way to revoke access to this memory. For short-term sharing of e.g., arguments in memory, so-called *local* capabilities [12] (which reside in registers only) could be used. Alternatively, an enclave can check whether its shared memory has been released using the IsUnique instruction. Lastly, to repeatedly share nonconfidential memory that will never contain any security-critical capabilities, enclaves can simply share a read-only view of said memory.

Early EDeInit. Once all parties that wish to communicate with an enclave complete local attestation, there is no need to keep the enclave's entry in the TCB. This is possible as the TCB entry does not provide any hardware protection, but serves the purely informative purpose of linking otypes and enclave identities. Hence, enclaves can prematurely execute EDeInit to free TCB space and still operate correctly.

Secure communication without liveness checks. One interesting characteristic of enclave communication in our design is that we do not need to rely on liveness checks (such as the ones present in Sancus) during secure communication. The caller enclave can invoke the callee without verifying whether the callee enclave still exists,

and the callee returns to the caller without checking its liveness. We can afford to omit these checks because the alternative, namely both signing and encrypting messages, is very cheap (taking a single instruction, contrary to nonsymbolic solutions), and hence can be applied by default. The advantages of omitting liveness checks are that the hardware is simplified and any TOCTOU issues related to checking and then invoking an enclave are avoided.

**Two-way sandbox.** The spatial memory safety offered by capabilities naturally turns enclaves into *two-way sand-boxes* [22], meaning that other code running in the same address space is protected from the enclave: enclaves can only manipulate memory they have appropriate capabilities for. This prevents e.g. Boomerang attacks [23].

**Dynamic entry points.** Traditionally, enclaves either list their entry points at creation time or have standard, predefined entry points. As we reuse sealed pairs to enforce entry points, an enclave can create more entry points at runtime by creating a sealed pair. Such dynamically created entry points could be selectively shared with attested counterparties to avoid the need to re-attest them on subsequent calls. To avoid mixing parts of different pairs, the enclave either needs to use different otypes for different entry points or have an entry point identifier in each data section.

Relocatable enclaves. EInitData does not include the enclave's base into the hash, contrary to hashing in e.g., Sancus [9]. Consequently, a deployer is not required to know the memory address at which an enclave is located beforehand, providing greater ease in deployment. This does place the requirement of writing Position Independent Code (PIC) on the developer, but RISC-V has efficient support for this [24]. This design decision implies that multiple instances of the same enclave have the same identity. Fortunately, this poses no security risk, as these enclaves would have different otypes and are hence distinguishable locally. In the remote case, key derivation can include each enclave's otype to create different keys.

# 4. Implementation

We now discuss three different implementations of our design from Section 3: one RISC-V specification of the ISA extensions that is written at the instruction level, abstracting away from the hardware, one RISC-V hardware implementation for studying performance, and a prototypical implementation on the ARM Morello platform to show commercial feasibility.

# 4.1. Sail specification of the extended ISA

To obtain a more formal account of the architectural extensions proposed in Section 3.3, we created a software implementation of our design in Sail [25].

Sail is an ISA specification language used to formalize ISA semantics. On top of that, Sail models serve various purposes: documentation can easily be generated from them, emulators (in C and OCaml) can be derived from the source code, and definitions can be exported to various proof assistants to enable reasoning about properties of

the ISA. CHERI researchers heavily use Sail to formalize different architectural implementations, and hence contains an existing formalization of both 32-bit and 64-bit CHERI-RISC-V [26], on top of which we implemented extensions for CHERI-TrEE.

The Sail implementation of CHERI-TrEE is complete; all previously described architectural implementation details are included. The implementation inherits the characteristics of Sail-CHERI-RISC-V: both RV32 and RV64 implementations are supported in a modular fashion, the model does not support split register banks (instead, a single register bank is shared for both capabilities and integers), and the use of compressed CHERI Concentrate capabilities is mandatory. For our purposes, we were most interested in the emulation functionality. Because generating an assembler from a Sail specification is not yet supported, we also extended CHERI's fork of the LLVM compiler to support the newly added instructions. This allowed using the LLVM toolchain to compile assembly files into well-formed ELF-binaries that Sail's C-emulator can executed. We developed basic unit tests to check functional correctness of each new instruction, as well as a larger scenario test, and ran these on top of the C-emulator.

### 4.2. Proteus RISC-V CPU framework

To verify and evaluate our design, we implemented the primitives from Section 3.3 in hardware. We based our implementation on *Proteus*, our open-source RISC-V processor designed with configurability and extensibility as its main goals.

Proteus is heavily inspired by VexRiscv [27] and designed in SpinalHDL [28], a Scala-based Hardware Description Language (HDL). SpinalHDL is essentially an HDL code generator: Scala is used to generate an HDL description at runtime (using primitives provided by the SpinalHDL library), which is then converted to either Verilog or VHDL. Designs are simulated using an HDL simulator or synthesized on FPGAs.

Proteus uses a plugin architecture to configure and extend processors. At its core, Proteus provides pipeline stages and the ability to pass values from one stage to the next. The logic contained in stages is not fixed but can be configured through plugins. This allows for a lot of flexibility in, for example, the number of pipeline stages and the supported features (e.g., the RISC-V "M" extension is an optional plugin). Concretely, our implementation uses a classic 5-stage RISC pipeline consisting of an IF (Instruction Fetch), ID (Instruction Decode), EX (Execute), MEM (Memory Access), and WB (register Write Back) stage. The plugin system also enables the development of custom extensions without having to alter the core implementation files. Currently, Proteus provides plugins to implement inorder pipelines with support for RV32IM and machine mode. A powerful feature of Proteus is the concept of services, which allows plugins to provide customization points to other plugins. For example, the plugin that implements load and store instructions offers an interface to intercept the generated addresses. This is used by one of our CHERI plugins to perform the necessary permission checks without having to modify the existing plugin.

We extended Proteus with plugins implementing most of version 8 of the CHERI-RISC-V 32-bit specifica-

tion [12]. It implements a split register file, capability manipulation, implicit memory access through *DDC* (the *Default Data Capability* register [12]) and *PCC* (the *Program Counter Capability* register [12]), explicit memory access through capabilities, exception handling, and storing capabilities in memory. To track capabilities in memory, an on-chip tag table is maintained that stores one tag-bit per capability-aligned word.

CHERI Proteus is not compliant with the CHERI specification in terms of the memory representation of capabilities: Instead of compressed capabilities (which are mandatory for RISC-V), Proteus uses a full-precision representation, which is easier to implement but causes in-memory capabilities to use 128 bits instead of 64 bits for CHERI-RISC-V 32 bit. This has the advantage that we have ample otype space for enclave seals (cf. Section 3.3). This also means we currently cannot take full advantage of the CHERI compiler toolchain, but are limited to the use of the assembler. However, this is sufficient to run complex software examples (see Section 5.1).

# 4.3. Implementing CHERI-TrEE on Proteus

To implement our design (Section 3.3), a number of components have to be added to the CPU core. To store the TCB state of enclaves, we add a table (EidTable), in which each entry stores the eid and identity (I) of an enclave. Entries also keep track of the current state of the enclave, which can be allocated (EInitCode has been called but EInitData not yet), ready (enclave fully initialized), or empty (the entry does not contain any enclave information). The table provides an interface to allocate a new entry (which increases the eid counter, see Section 3.3), retrieve an existing entry (used by EInitData), and to finalize an entry by storing I. When searching, EidTable iterates through the entries one by one. Note that the table size is parameterized and implemented as a plugin, allowing us to easily create an alternative implementation (e.g., one that stores entries in memory) without changing the rest of the design. To calculate enclave identities, we use a SHA256 implementation from the SpinalCrypto library [29].

As EInitData needs access to the memory bus, we decided to implement all new instructions in the MEM stage of the 5-stage pipeline. All instructions are based on state machines of varying complexity. EInitCode simply asks EidTable to allocate a new entry and, if successful, seals its input capability with o\_entry (Section 3.4). EInitData is by far the most complex instruction to implement, as it needs to scan all registers and memory for overlapping capabilities. After performing sanity checks on its inputs (e.g., whether the code capability corresponds to an entry in EidTable), it starts by requesting exclusive access to the pipeline. This operation makes sure that the requesting instruction is the only one executing in the pipeline by flushing or invalidating stages containing other instructions. This is necessary to correctly perform the register scanning as otherwise, copies of registers might be available in pipeline stages. While having exclusive access, the state machine iterates over all general purpose and special capability registers to verify that there are no overlaps with the code or data capability of the enclave.

To scan memory, we use a service from the CHERI plugins. This service accesses the tag storage to produce addresses of valid capabilities without the need to perform memory loads. It currently only checks a single tag-bit per cycle, leaving room for future optimizations. Once we encounter a capability, we load it and check for overlap. If there are no overlapping capabilities, the hash of the code section is calculated by loading its contents word-byword and providing it to the SHA256 block. The result is then stored in EidTable and the corresponding entry is marked as *ready*. Finally, the sealing capability is created and stored at the first address of the data section.

EstoreId checks that the hash fits in its input capability and iterates over the entries of EidTable to find the entry corresponding to the given seal. If it finds one and it is marked as *ready*, the hash is written to memory.

# 4.4. Implementation on ARM Morello

We implemented CHERI-TrEE on the first commercial CHERI-enabled processor, ARM Morello [3], firstly using ARM's FVP simulator, and then on the hardware when it became available. As noted before, the Morello architecture does not necessarily represent the typical embedded processor we envision for CHERI-TrEE; yet, we still use it as an implementation platform to show the feasibility of our design on the only commercial capability machine.

While for Proteus we realized functionality as an ISA extension, here we show that it is also feasible to implement CHERI-TrEE in (low-level) software: On Morello, one can use the Exception Level 3 (EL3) monitor or the EL2 hypervisor to pause (at least in a single-core scenario) an OS running at EL1 to perform the CHERI-TrEE operations, including the memory sweep. We built a small trusted hypervisor at EL2 to implement CHERI-TrEE operations, defining hypervisor calls to trigger an exception to EL2. The inputs are held in the first two registers on entry to EL2, and then passed on as parameters in the handler code. For the register sweep, all EL1 register values are saved on the EL2 stack following a hypervisor call. A capability pointing to this stack is passed through to the exception handler function so that the sweep is performed on the state of EL1 registers. The registers are restored on return, except for the overwritten return values.

Our implementation closely resembles the Proteus implementation, for ease of testing and comparison. Differences in hardware however inevitably lead to deviations. For example, unlike the RISC-V implementations, hypervisor calls on Morello are not limited to two inputs and one output, enabling several improvements. These include having a single initialization instruction EInit, and initializing a group of enclaves at the same time. The latter variant is particularly beneficial due to the size of memory on the Morello platform: a substantial amount of time is spent on the memory sweep, checking for the presence of capabilities. Because the relative amount of time spent on checking for overlaps is small, the initialization time can be halved for a two-enclave system using this approach (or proportionally reduced for a larger number of enclaves). We implemented this variant on Morello as an optional feature by defining the number of enclaves to be initialized in a single block, and passing the required number of enclave capabilities to the hypervisor.

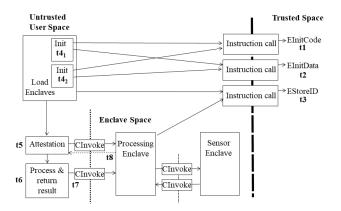

Figure 3. Benchmark setup showing measurements made for both micro and macro benchmarks.

Supporting virtual memory in ARM Morello poses additional challenges: a malicious OS at EL1 could give up ownership of an enclave capability, but then re-map another virtual address (and hence different capability) to again point to that enclave's physical memory. This issue can be overcome by either fully blocking changes to the page tables by EL1 (while the enclave is executing) and/or through appropriate MMU memory permissions and register access restrictions set at EL2. This is included in the prototype by setting bits in the hypervisor control register to block manipulation of EL1 system registers that could cause MMU changes. As the hypervisor is in control of the set up of the page tables for EL1, it is also possible to make the page table area in memory read only. However, both solutions preclude integrating the design with a rich OS using virtual memory. Yet, we note that the CHERI-TrEE design would be a promising candidate to use as the basis for a trusted OS inside ARM Trustzone, similar to the approach taken by Komodo [11], but with the shown benefits of a capability-based system.

# 5. Evaluation

Next, we evaluate the performance and (hardware) implementation costs of CHERI-TrEE on different platforms: our Proteus (Sections 5.1 and 5.2) and the ARM Morello simulator and the actual prototype hardware (Section 5.3).

# 5.1. Performance on Proteus

We conducted a number of micro and macro performance benchmarks. The micro benchmarks quantify the cost of individual instructions, while the macro benchmark measures the overhead on a full application consisting of multiple enclaves. Fig. 3 summarizes the setup of the macro benchmark and indicates the time measurements made for both micro and macro benchmarks, which we will reference in the following.

Micro benchmarks. The micro benchmarks respectively measure t1, t2 and t3 from Fig. 3. The runtime of EInitCode solely depends on the current occupation of the EidTable. Executing it with an empty table takes 4 cycles, and one extra cycle is needed for every non-empty entry at the beginning of the table. For EInitData, there is a fixed and a variable cost. The fixed part consists of

getting exclusive access over the pipeline (one cycle) and scanning registers for overlapping capabilities (one cycle per register). The variable cost consists of multiple parts: First, the entry corresponding to the code capability needs to be looked up in EidTable. Second, memory needs to be scanned for overlapping capabilities. As mentioned in Section 4.3, tag-bits are scanned at a rate of one per cycle, so to get all addresses containing capabilities, the amount of cycles needed is the memory size divided by the size of a capability (128 bits). Then, for each capability, a capability load needs to be performed, which takes 4 cycles. The last variable part is creating the enclave's identity by hashing its code section. Table 1 shows the measured performance of EInitData. The execution time of EStoreId depends on the size of the hash and the index of the hash in EidTable, as it has to be searched for the correct hash. For the initial enclave, we measured execution time to be 19 cycles. We did not perform micro benchmarks for enclave calls or secure communication, as these use the pre-existing CInvoke and CSeal/CUnseal instructions, and hence incur the same overhead as unaltered CHERI.

TABLE 1. CYCLE COUNT OF EINITDATA (t2). RAM STATE IS SIZE (IN KIB) PLUS NUMBER OF VALID CAPABILITIES IN MEMORY.

|           | Code size (B) |        |        |  |  |

|-----------|---------------|--------|--------|--|--|

| RAM state | 256           | 512    | 1024   |  |  |

| 128+0     | 8811          | 9271   | 10,191 |  |  |

| 128+100   | 9211          | 9671   | 10,591 |  |  |

| 256+0     | 17,003        | 17,463 | 18,383 |  |  |

| 256+100   | 17,403        | 17,863 | 18,783 |  |  |

**Macro benchmark.** To measure the performance of a more realistic application, we built a scenario where two enclaves communicate with each other (cf. Fig. 3). A "sensor enclave" provides an entry point to read the (encrypted and signed) value of a sensor, e.g., input from a camera or microphone. The "processing enclave" attests the sensor enclave, gets a sensor reading (e.g., an audio sample from a microphone), and performs some operation on the value (e.g., some filtering or similar digital processing).

To correctly initialize enclaves, untrusted code first sets up a bump memory allocator that uniquely owns a region of memory. The untrusted code then relocates the code of both enclaves to a uniquely-owned region and allocates data sections for them. It registers these using EInitCode and EInitData (t41 and t42 in Fig. 3) and invokes their initialization routines as described in Section 3.3. After sanity checks, the stack pointer is initialized and stored in the data section. As the last step, the public parts of the sign and encryption seals are derived from the seal stored by EInitData and returned.

Next, the processing enclave attests the sensor enclave (t5 in Fig. 3)): it provides an entry point to receive the entry capabilities and public seals of the sensor from untrusted code. To support multiple entry points, enclaves dispatch based on the value in an agreed-upon register. One specific value is used as a "return" entry point, which is invoked when returning from a call. The actual identity of the sensor enclave is fetched through EStoreId and compared to the precomputed identity stored in the code

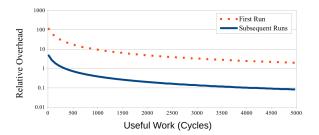

Figure 4. Relative overhead (with and without initialization and attestation) of sensor use compared to an unprotected scenario. Plotted in terms of useful work performed in the sensor enclave.

TABLE 2. TIMINGS FOR OUR MACRO BENCHMARK: "INIT" INCLUDES EINITCODE/DATA, INVOKING ENCLAVE INITIALIZATION CODE AND PREPARATION (E.G., CLEARING REGISTERS). "SENSOR USE" INCLUDES THE PROCESSING TO SENSOR ENCLAVE ROUND-TRIP

| Step                                       | Runtime (cycles) |

|--------------------------------------------|------------------|

| Init processing enclave (t4 <sub>1</sub> ) | 9773             |

| Init sensor enclave (t4 <sub>2</sub> )     | 9163             |

| Attestation (t5)                           | 384              |

| Sensor use (t6)                            | 471              |

section. If the identity is correct, the processing enclave stores the entry capabilities and seals of the sensor.

The actual application (t6 in Fig. 3)) starts by calling the "use sensor" entry point of the processing enclave. The processing enclave stores the nonce and the public part of its encryption seal in a buffer, leaving space for the return value, and encrypts the buffer using the sensor's encryption seal. It then calls the sensor enclave with its own entry capabilities as the return pointer. The sensor decrypts the input capability and stores a sensor reading in the buffer. In our prototype, we simulate such a device by storing an arbitrary value as sensor reading. The sensor then encrypts the capability to the buffer with the caller's encryption seal and signs the result using the methodology from Fig. 2. Upon return, the processing enclave verifies the signature and nonce and decrypts the returned capability. Then, it processes (currently simply doubling) the reading, before returning it to the caller.

We ran this scenario bare-metal on a cycle-accurate Verilator-based [30] simulation of CHERI-TrEE with 128KiB of RAM. The code size of the processing enclave is 656 bytes, while that of the sensor enclave is 336 bytes. The deterministic execution times of the different steps of our scenario are shown in Table 2. For comparison, executing an "unprotected" version of our scenario (where no enclaves are used and arguments are passed without sealing or signing) took 79 cycles. The one-time cost of initialization of enclaves makes up the bulk of the execution time. Overhead compared to the unprotected case is large, since little computation is performed in this scenario. Taking inspiration from Sancus, we therefore reran the macro benchmark for different amounts of useful work performed by the sensor enclave. Fig. 4 shows how the overhead relative to the unprotected scenario quickly decreases as the sensor enclave's useful work increases.

TABLE 3. IMPLEMENTATION RESULTS FOR THE PROTEUS PROCESSOR AND ITS VARIANTS ON THE ZYNQ ULTRASCALE+ XCZU9EG-2FFVB1156 FPGA BOARD WITH 128 KIB MEMORY. PERCENTAGES INDICATE AREA USAGE RELATIVE TO TOTAL FPGA SIZE.

| Processor (128 | Area occupation    |             |           |      |              | Operating   | Dynamic    |

|----------------|--------------------|-------------|-----------|------|--------------|-------------|------------|

| KiB memory)    | LUTs               | Flip-flops  | BRAMs     | DSPs | CLBs         | freq. (MHz) | power (mW) |

| Proteus        | 3054 (1.1%)        | 1663 (0.3%) | 32 (3.5%) | -    | 694 (2.03%)  | 180         | 40         |

| CHERI Proteus  | 8059 (2.94%)       | 3915~(0.7%) | 32(3.5%)  | -    | 1298(3.79%)  | 70          | 23         |

| CHERI-TrEE     | $12,806 \ (4.7\%)$ | 7514 (1.4%) | 32 (3.5%) | -    | 2385 (6.96%) | 70          | 69         |

# 5.2. Hardware implementation of Proteus

To quantify the performance and resource requirements of the Proteus processor, we implemented and ran it using the Xilinx Vivado tools [31] on a Zynq UltraScale+XCZU9EG FPGA [32]. We extended the Verilog file generated by SpinalHDL with support circuitry (e.g., for clocking) and set up constraints and pin connections for our FPGA board. We considered Proteus (without capabilities); CHERI Proteus (with capabilities); and the EES-enabled variant, CHERI-TrEE. We used common metrics to analyze the result: area occupation, operating frequency, and power consumption. Table 3 presents the results. In Section A, we also compare Proteus and variants to the CHERI Piccolo processor developed in Cambridge [33].

First, we evaluated the impact of adding CHERI and CHERI-TrEE functionality. Table 3 confirms that area occupation increases with processor complexity. CHERI Proteus uses more hardware primitives than Proteus, occupying  $\approx 1.87\times$  more FPGA area in terms of Configurable Logic Blocks (CLBs). This increase in area occupation is largely caused by CHERI capabilities and tag-bits, which are implemented with distributed RAM and hence realized as LUTs. Similarly, CHERI-TrEE uses  $\approx 1.84\times$  more CLBs than CHERI Proteus. The SHA256 block is a big factor in this increase. However, this block's cost can potentially be amortized, for example when it is reused to accelerate cryptographic instructions. All variants use 32 Block Random Access Memories (BRAMs), because they have the same 128 KiB memory size.

Regarding performance, the CHERI Proteus processor and its CHERI-TrEE variant decrease the maximum clock frequency by  $\approx 2.57 \times$  compared to Proteus. As expected, adding capabilities substantially increased the processor's complexity. This is due to the CHERI trap and exception handling circuits deployed with logical primitives on the critical path. We note that we did not specifically optimize the hardware design for maximum clock frequency; thus, substantial improvements are likely possible, e.g., by adding register stages in the critical path. Finally, CHERI Proteus has a 74% lower dynamic power consumption than Proteus as it runs at a lower clock frequency. Conversely, due to its higher resource usage, CHERI-TrEE consumes 69 mW, i.e., 72.5% more.

In summary, our Proteus core and its capability/EES variants scale well and largely independently of the memory size, requiring  $\leq 7\%$  of the total area on our FPGA. We also deployed the CHERI Proteus and CHERI-TrEE variants on the low-end Arty A7-35T XC7A35TICSG324-1L FPGA. CHERI Proteus used 28.23% of the available area, while CHERI-TrEE occupied 51.57%, which shows that our design can also be implemented on small FPGAs.

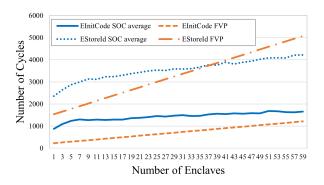

Figure 5. Measured number of clock cycles to run Elnitcode and ElnitData for the Sensor Enclave on Morello FVP / hardware (SOC).

### 5.3. Performance on ARM Morello

Micro benchmarks. The number of clock cycles for EInitCode, EInitData, and EStoreID at EL2 (t1, t2 and t3 in Fig. 3) was measured on both the Morello FVP and the hardware (SOC) using Arm's Performance Monitor cycle counter. The full HVC calls take longer because firstly an exception is called to change EL and then the exception handler needs to determine which HVC function to run. Measurements on the hardware were averaged over 100 runs, because we observed some variation in results between runs of the same binary, likely due to factors such as the data and instruction caches. Fig. 5 shows a graph of EInitCode and EInitData for the sensor enclave over an increasing number of enclaves. The runtime is affected by the number of table entries searched.

For EInitData however, the predominant cost is the memory sweep and therefore the increase in the number of clock cycles over a larger number of enclaves is relatively small. On the Morello FVP, an EL1 memory sweep by the EL2 hypervisor took about 2.16M clock cycles per MB of DRAM, corresponding to 1.1 ms/MB on a single core running at 2 GHz. This includes overlap checks of the 233 capabilities that were detected in our example. A "clean" memory sweep (no capabilities) is only marginally faster because if the tag-bit is not set there is no need for an overlap check. Given the sweep is performed on 16 bytes at a time (capabilities are aligned to 16-byte boundaries), this corresponds to approx. 33 cycles to check each capability memory location. Performance on the hardware returned similar results: 2.15M clock cycles per MB (without outputting number of overlap checks).

**Macro benchmark.** We ran the same macro benchmark as for Proteus. Since the initialization time of the enclaves is dominated by the memory sweep we do not repeat the

TABLE 4. EXECUTION TIMES ON MORELLO MACRO BENCHMARK.

| Step                         | FVP (cycles) | SOC (av. cycles) |

|------------------------------|--------------|------------------|

| Attestation (t5)             | 2026         | 1938             |

| Sensor use (t6)              | 255          | 206              |

| Enclave function entry (t7)  | 69           | 114              |

| Enclave function return (t8) | 31           | 53               |

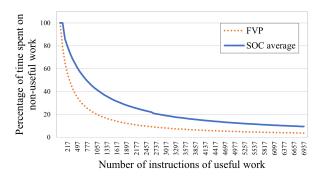

Figure 6. Percentage of time spent on non-useful work to process and return sensor data from the enclaves on Morello FVP / hardware (SOC).

figures here. Instead, Table 4 additionally measures the boundary timings for going into and out of the enclave (t7 and t8 in Fig. 3). t7 is the number of clock cycles to go from the calling function to the entry point of the desired function within the enclave and includes the invoke instruction, setting up registers and stack, and jumping to the function within the enclave. t8 is the number of clock cycles it takes to return and includes some stack and register manipulation as well as the actual return instruction. We re-ran the macro benchmark for different amounts of useful work performed by the sensor enclave, measuring the time to process and return the results (t6). Fig. 6 shows the percentage of time spent on non-useful work for increasing amounts of useful work.

While we demonstrated that CHERI-TrEE can run on a processor like Morello, the potentially larger memory size means a greater time cost of the sweep operation—especially if the large DRAM of several GB is to be fully used. However, this can be mitigated to some extent by the aforementioned grouping of enclaves during the initialisation process (cf. Section 4.4). Section 6 discusses further improvements and alternatives to the memory sweep.

### 6. Further extensions and future work

Being a research prototype, CHERI-TrEE allows for various extensions and follow-up work.